# **ELECTRICAL TECHNOLOGY**

# GUIDELINES FOR PRACTICAL ASSESSMENT TASKS

2018

These guidelines consist of 79 pages.

# **TABLE OF CONTENTS**

| 1.                                                                          | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3                                                              |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 2.                                                                          | TEACHER GUIDELINES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5                                                              |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8                        | How to administer the PATs How to mark/assess PATs PAT assessment management plan Moderation of the PATs Absence/Non-submission of tasks Simulations Projects Working mark sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5<br>5<br>6<br>7<br>7<br>8<br>8                                |

| 3.                                                                          | LEARNER GUIDELINES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10                                                             |

| 3.1<br>3.2                                                                  | Instructions to the learner Declaration of authenticity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11<br>11                                                       |

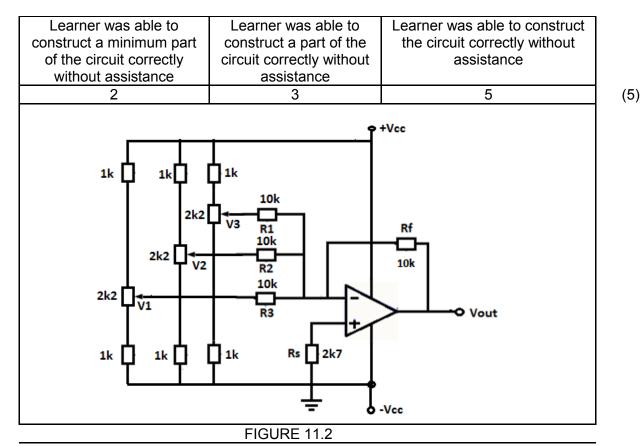

| 4.                                                                          | SECTION A: SIMULATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12                                                             |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11 | Simulation 1: RLC circuit Simulation 2: Connecting three single-phase transformers to a three-phase supply Simulation 3: Inspecting and testing the AC motor Simulation 4: DOL starter Simulation 5: Three-phase sequence motor control starter with overload and timer using PLC Simulation 6: The field-effect transistor Simulation 7: Amplifiers using a JFET and a Darlington pair Simulation 8: Two-stage RC amplifier and an RC phase-shift oscillator Simulation 9: 741 Op-amp and 555 IC Simulation 10: Bi-stable multivibrator and an LED sequencer Simulation 11: 741 Op-amp Schmitt trigger and summing amplifier circuit | 12<br>19<br>22<br>25<br>28<br>32<br>38<br>44<br>50<br>56<br>62 |

| 5.                                                                          | SECTION B: DESIGN AND MAKE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66                                                             |

| 5.1<br>5.2<br>5.3<br>5.4                                                    | Design and make: Part 1 Assessment of the design-and-make phase: Part 1 Design and make: Part 2 Assessment of the design-and-make phase: Part 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 68<br>72<br>74<br>76                                           |

| 6.                                                                          | PROJECTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 77                                                             |

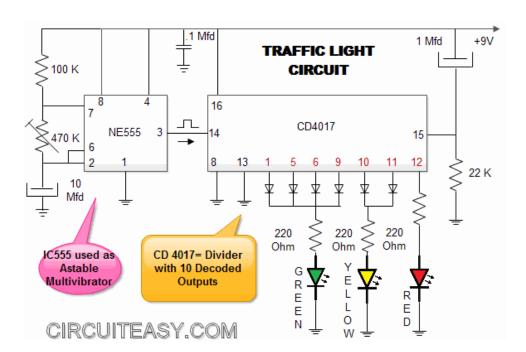

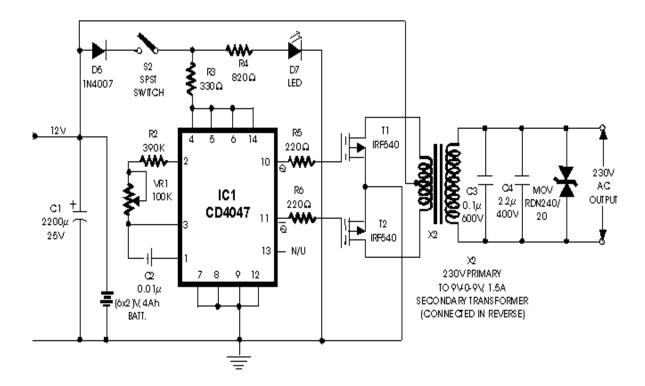

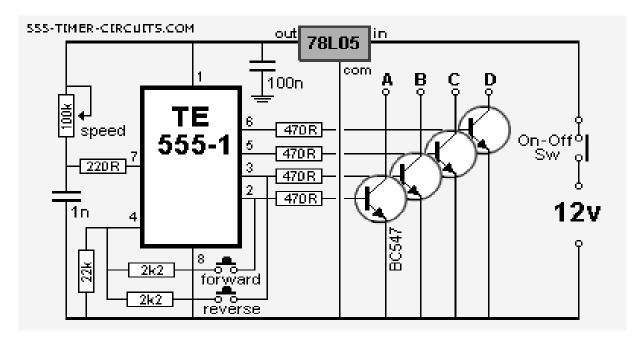

| 6.1<br>6.2<br>6.3                                                           | Practical project 1: Inverter 110 W 12 VDC to 230 V by IC 4047 – IRF540 Practical project 2: Stepper motor speed control TE 555-1 Practical project (electronics): Traffic light                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 77<br>78<br>79                                                 |

#### 1. INTRODUCTION

The 16 Curriculum and Assessment Policy Statement subjects which contain a practical component all include a practical assessment task (PAT). These subjects are:

AGRICULTURE: Agricultural Management Practices, Agricultural

Technology

ARTS: Dance Studies, Design, Dramatic Arts, Music,

Visual Arts

SCIENCES: Computer Applications Technology, Information

Technology

SERVICES: Consumer Studies, Hospitality Studies, Tourism

TECHNOLOGY: Civil Technology, Electrical Technology, Mechanical

Technology and Engineering Graphics and Design

A practical assessment task (PAT) mark is a compulsory component of the final promotion mark for all candidates offering subjects that have a practical component and counts 25% (100 marks) of the end-of-year examination mark. The PAT is implemented across the first three terms of the school year. This is broken down into different phases or a series of smaller activities that make up the PAT. The PAT allows for learners to be assessed on a regular basis during the school year and it also allows for the assessment of skills that cannot be assessed in a written format, e.g. test or examination. It is therefore important that schools ensure that all learners complete the practical assessment tasks within the stipulated period to ensure that learners are resulted at the end of the school year. The planning and execution of the PAT differs from subject to subject.

Practical assessment tasks are designed to develop and demonstrate a learner's ability to integrate a variety of skills in order to solve a problem. The PAT also uses a technological process to inform the learner what steps needs to be followed to derive a solution for the problem.

The 2018 PAT has three focus areas with projects and simulations in each of the following fields:

- Electrical

- Electronics

- Digital Electronics

The PAT consists of four simulations and a practical project. The teacher may choose any of the practical projects and use a combination of the simulations available.

The teacher has to apply assessment on an on-going basis at the same time that the learner is developing the required skills. Four simulations should be completed by the learners, in addition to the manufacturing of a practical project.

The PAT incorporates all the skills the learner has developed from Grades 10, 11 and 12. The PAT ensures that all the different skills will be acquired by learners on completion of practical work, that is electrical, electronics and digital electronics as well as the correct use of tools and instruments.

#### Requirements for presentation

A learner must present the following:

- PAT file with all the evidence of simulations, design and prototyping. A copy of the PAT 2018 cover page and the relevant simulations and assessment sheets should be given to each learner to include in the file.

- Practical project with:

- Enclosure

- The file must include a design.

- The enclosure and the design must match.

- No cardboard boxes are allowed.

- Plastic and metal enclosures are acceptable.

- The enclosure should be accessible for scrutiny inside.

- Lids that are secured with screws are preferred.

- Circuit board

- The file should include the PCB design.

- The PCB must be mounted inside the enclosure in such a manner that it can be removed for scrutiny.

- Switches, potentiometers, connectors and other items must be mounted.

- Wiring must be neat and bound/wrapped.

- Wiring must be long enough to allow for the PCB to be removed and inspected with ease.

- Logo and Name

- The file should contain the logo and name design.

- Logo and name must be prominent on the enclosure.

The PAT will have a financial impact on the school budget and school management teams are required to make provision to accommodate this particular expense.

PAT components and other items must be acquired timely for use by the learners before the end of the first term at the start of the academic year.

It is the responsibility of the HOD to ensure that the teacher is progressing with the PAT from the start of the school year.

Provincial departments are responsible for setting up moderation timetables and consequently PATs should be completed in time for moderation.

#### 2. TEACHER GUIDELINES

#### 2.1 How to administer the PATs

Teachers must ensure that learners complete the simulations required for each term. • The project should be started in January in order to ensure its completion by August. All formal assessment is the teacher's responsibility.

The PAT should be completed during the first three terms and must be ready at the start of PAT moderation. Teachers must make copies of the relevant simulations and hand them to learners at the beginning of each term.

The PAT must not to leave the workshop and must be kept in a safe place at all times when the learner is not working on it.

Adhere to the weightings of the PAT and teachers are not allowed to change the weightings for the different sections.

#### 2.2 How to mark/assess the PATs

The PAT for Grade 12 is externally set and moderated, but internally assessed. All formal assessment will be done by the teacher.

The teacher is required to produce a **working model and model answer file** which sets the baseline for assessment at a Highly Competent Level for every project choice exercised by the learners. This file must include all the simulations with answers the teacher has done him-/herself. The teacher will use the model answers and project to assess the simulations and projects of the learners.

Once a facet sheet has been completed by the teacher, assessment will be deemed to be complete. No re-assessment will be done once the facet sheets have been completed and captured by the teacher. Learners must ensure that the work is done to the standard required before the teacher finally assesses the PAT during each stage of completion.

# 2.3 PAT assessment management plan

The assessment plan for the PAT is as follows:

| TIME FRAME                 | ACTIVITY                                              | RESPONSIBILITY                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | Preparation for PAT 2018                              | Teacher – Builds the models and works out the model answers for the simulations for 2018. Identify shortages in tools, equipment and consumable items for simulations which must be procured in 2018.  SMT – Receive procurement requests from teachers and process payments for the acquisition of required items.                                                 |

| January–March<br>2018      | Simulations<br>1 and 2                                | Teacher – Copies and hands out simulations.  Learners – Complete simulations.  Teacher – Assesses simulations.  HOD – Checks if tasks have been completed and marked by the teacher before the holiday.                                                                                                                                                             |

| January 2018               | PAT Project:<br>Procurement                           | Teacher – Obtains quotations for PAT projects.  Principal – Approves PAT procurement for PAT projects.  Teacher – Ensures that PAT projects are ordered and delivered.  HOD – Checks up on teacher to see if the process is being adhered to.                                                                                                                       |

| February 2018              | PAT Project:<br>Learners<br>commence with<br>project. | Teacher – Ensures that there is secure storage for PAT projects.  Teacher – Hands out and takes in PAT projects.  Teacher – Includes practical sessions for learners to complete PAT project every week.  Learners – Commence with completion of the PAT project.  HOD – Checks on teacher to ensure that practical workshop sessions take place on a weekly basis. |

| April–June 2018            | Moderation of Simulations 1 and 2                     | District Subject Facilitator/Subject Specialist will visit the school and moderate Simulations 1 and 2. 10% of learners' work is moderated.                                                                                                                                                                                                                         |

| April–June 2018            | Simulations<br>3 and 4                                | Teacher – Copies and hands out simulations.  Learners – Complete simulations.  Teacher – Assesses simulations.  HOD – Checks if tasks have been completed and marked by the teacher before the holiday.                                                                                                                                                             |

| April–June 2018            | PAT project:<br>Learners<br>continue with<br>project  | Teacher – Ensures that there is secure storage for PAT projects.  Teacher – Hands out and takes in PAT projects.  Teacher – Includes practical sessions for learners to complete PAT project every week.  Learners – Continue with completion of the PAT project.  HOD – Checks on teacher to ensure that practical workshop sessions take place on a weekly basis. |

| July August                | PAT intervention Moderation of                        | Learners that are behind on the PAT are required to complete the project during this holiday.  District Subject Facilitator/Subject Specialist will visit the school                                                                                                                                                                                                |

| July–August<br>2018        | Simulations<br>3 and 4                                | and moderate Simulations 3 and 4. Different learners from the previous term. 10% of learners' work is moderated.                                                                                                                                                                                                                                                    |

| July–August<br>2018        | PAT project:<br>completion                            | Teacher – Ensures that there is secure storage for PAT projects.  Teacher – Hands out and takes in PAT projects.  Teacher – Completes the PAT project with learners and compiles the PAT file.  Learners – Complete the PAT project and file.  HOD – Checks to see that 100% of PAT files and project are completed and assessed                                    |

| September–<br>October 2018 | PAT<br>moderation                                     | PAT projects are moderated by subject facilitators/subject specialists from the province and learners are available to demonstrate skills. 10% of learners are moderated at random.                                                                                                                                                                                 |

#### 2.4 Moderation of the PATs

Provincial moderation of each term's simulations will start as early as the following term. Simulations 1 and 2 should be moderated as soon as the second term starts. Similarly simulations 3 and 4 will be moderated in July. The project, however, will only be moderated on completion.

During moderation of the PAT the learner's file and project must be presented to the moderator.

The moderation process is as follows:

- During moderation learners are randomly selected to demonstrate the different simulations. All four simulations will be moderated.

- The teacher is required to build an exemplar model for each project type chosen for the school.

- This model must be on display during moderation.

- The teacher's model forms the standard of the moderation at Level 4 (Highly Competent).

- Level 5 assessments must exceed the model of the teacher in skill and finishing.

- Learners being moderated will have access to their file during moderation and may refer to the simulations they completed earlier in the year.

- Learners may not ask assistance from other learners during moderation.

- All projects and files must be on display for the moderator.

- If a learner is unable to repeat the simulation or cannot produce a working circuit during moderation, marks will be deducted and circuits assessed as not being operational.

- The moderator will select, at random, not fewer than **two projects** (not simulations) and the learners involved will have to explain how the project was manufactured.

- Where required, the moderator should be able to call on the learner to explain the function and principles of operation and also request the learner to exhibit the skills acquired through the simulations for moderation purposes.

- On completion, the moderator will, if needed, adjust the marks of the group upwards or downwards, depending on the outcome of moderation.

- Normal examination protocols for appeals will be adhered to if a dispute arises from adjustments made.

#### 2.5 Absence/Non-submission of tasks

In the absence of a PAT mark in Electrical Technology, without a valid reason, the learner will be given three weeks before the commencement of the final end-of-year examination to submit the outstanding task(s). Should the learner fail to fulfil the outstanding PAT requirement such a learner will be awarded a zero (0) for that PAT component.

#### 2.6 Simulations

Simulations are circuits, experiments and tests which the learner will have to build, test and measure and do practically as part of the development of practical skills. These skills have to be illustrated to the external moderator who visits the school at intervals during the school year.

Teachers who use simulation programs on computer are welcome to use them for the learners to practise on. However, it is required that the circuit be built using real components and that measurements be made with actual instruments for the purposes of assessment and moderation.

The correct procedure to complete simulations is outlined below for teachers and school management teams who are responsible for the implementation of the PAT in Electrical Technology.

- **Step 1:** The teacher will choose simulations from the examples provided.

- Step 2: Compile a list of the components needed for every simulation. Add extra components as these items are very small and you will need extras because they are lost or damaged very easily when learners work with them.

- **Step 3:** Contact three different electronics component suppliers for comparative quotations.

- **Step 4:** Submit the quotations to the SMT for approval and procurement of the items.

- Step 5: Store the components. Collate items for each simulation, thus making it easier to distribute and use during practical sessions. Ensure that different values of components do not mix as this will lead to components being used incorrectly. This could damage the component and, in extreme cases, the equipment used.

- **Step 6:** Copy the relevant simulations and hand them out to learners at the start of the term.

Teachers are allowed to adjust circuits and component values to suit their environment/resource availability.

Teachers are required to develop a set of model answers in the teacher's portfolio.

Moderators will use the teacher's model answers and artefact when moderating.

#### 2.7 **Projects**

The projects are construction projects teachers can choose for their learners. These projects are based on circuits provided by schools and subject advisors. The projects are based on working prototypes and require careful construction in order for it to operate correctly.

Projects vary in cost and teachers must ensure that the projects chosen fall within the scope of the school's budget.

Once the teacher has decided on a circuit, he/she must construct the prototype. Thereafter copies of the circuit provided can be made and distributed to learners. They MUST redraw these circuits in their portfolios correctly.

The description of the operation of the circuits is NOT complete. Learners are required to interrogate the function of the components in the circuit provided. They should elaborate on the purpose of components in the circuit. It is recommended that learners investigate similar circuits available on the internet and in the school library/workshop reference books.

DBE/PAT 2018

2.8 **Working mark sheet**(A working Excel file is provided with this PAT.)

| PAT | Mark Sheet      | Ter                   | m 1                   | Ter             | m 2             | Pro                                   | ject                                  |                                                  |                 | ¥              |

|-----|-----------------|-----------------------|-----------------------|-----------------|-----------------|---------------------------------------|---------------------------------------|--------------------------------------------------|-----------------|----------------|

| No. | Name of Learner | Simulation<br>1<br>40 | Simulation<br>2<br>40 | Simulation<br>3 | Simulation<br>4 | Design<br>and<br>Make<br>Part 1<br>70 | Design<br>and<br>Make<br>Part 2<br>20 | Total =<br>Term1 +<br>Term 2 +<br>Project<br>250 | Mark out of 100 | Moderated Mark |

| 1   |                 |                       |                       |                 |                 |                                       |                                       |                                                  |                 |                |

| 2   |                 |                       |                       |                 |                 |                                       |                                       |                                                  |                 |                |

| 3   |                 |                       |                       |                 |                 |                                       |                                       |                                                  |                 |                |

| 4   |                 |                       |                       |                 |                 |                                       |                                       |                                                  |                 |                |

| 5   |                 |                       |                       |                 |                 |                                       |                                       |                                                  |                 |                |

| 6   |                 |                       |                       |                 |                 |                                       |                                       |                                                  |                 |                |

| 7   |                 |                       |                       |                 |                 |                                       |                                       |                                                  |                 |                |

| 8   |                 |                       |                       |                 |                 |                                       |                                       |                                                  |                 |                |

| 9   |                 |                       |                       |                 |                 |                                       |                                       |                                                  |                 |                |

| 10  |                 |                       |                       |                 |                 |                                       |                                       |                                                  |                 |                |

| 12  |                 |                       |                       |                 |                 |                                       |                                       |                                                  |                 |                |

| 13  |                 |                       |                       |                 |                 |                                       |                                       |                                                  |                 |                |

| 14  |                 |                       |                       |                 |                 |                                       |                                       |                                                  |                 |                |

| 15  |                 |                       |                       |                 |                 |                                       |                                       |                                                  |                 |                |

| . • | Total           |                       |                       |                 |                 |                                       |                                       |                                                  |                 |                |

|     | Average         |                       |                       |                 |                 |                                       |                                       |                                                  |                 |                |

| Teacher Name: | Principal Name: | Moderator Name: |              |

|---------------|-----------------|-----------------|--------------|

| Signature:    | Signature:      | Signature:      | School Stamp |

| Date:         | Date:           | Date:           |              |

# **NSC**

#### 3. **LEARNER GUIDELINES**

**PAT 2018 Cover Page** (Place this page at the front of the PAT.)

# **Department of Basic Education** Grade 12 **CAPS for Technical High Schools Practical Assessment Task – Electrical Technology**

Time Allowed: Term 1 to Term 3 (2018)

| Class:                                     |                                                                        |

|--------------------------------------------|------------------------------------------------------------------------|

| School:                                    |                                                                        |

| Specialisation (Tick your special          |                                                                        |

| Electrical (Power Systems) - Electronics - | □(Simulation 1, 2, 3, 4, 5 and 6) Any 4<br>□(Simulation 1, 2, 7 and 8) |

| Electronics -                              | □(Simulation 1, 2, 7 and 8)                                            |

# **Evidence of Moderation:**

NOTE: When the learner evidence (LE) selected has been moderated at school level, the table will contain evidence of moderation. Provincial moderators will sign the provincial moderation and only sign if re-moderation is needed.

| Moderation            | Signature | Date | Signature     | Date |

|-----------------------|-----------|------|---------------|------|

| School-based          |           |      |               |      |

| Provincial moderation |           |      | Re-moderation |      |

#### **Mark Allocation**

| PAT Component                       | Maximum mark | Learner mark | Moderated<br>mark |

|-------------------------------------|--------------|--------------|-------------------|

| Simulation 1                        | 50           |              |                   |

| Simulation 2                        | 50           |              |                   |

| Simulation 3                        | 50           |              |                   |

| Simulation 4                        | 50           |              |                   |

| Design and Make Project – Circuit   | 40           |              |                   |

| Design and Make Project – Enclosure | 10           |              |                   |

| Total                               | 250          |              |                   |

#### 3.1 **Instructions to the learner**

- This PAT counts 25% of your final promotion mark.

- All work produced by you must be your own effort. Group work and co-operative work are not allowed.

- The PAT must be completed over three terms.

- The PAT file must contain 4 simulations and a practical project.

- Calculations should be clear and include units. Calculations should be rounded off to TWO decimals. SI units should be used.

- Circuit diagrams may be hand-drawn or drawn on CAD. NO photocopies or scanned files are allowed.

- Photographs are allowed and may be in colour or grey scale. Scanned photographs and photocopies are allowed.

- Learners with identical photographs will be penalised and receive zero (0) for that section.

- This document must be placed inside your PAT file together with the other evidence.

| 3.2 | Declaration of authenticity (COMPULSORY) |                                                                                             |  |  |  |

|-----|------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|

|     | Declaration: I                           | (Name) herewith declare that the work rely my own effort. I understand that if proven held. |  |  |  |

|     | Signature of learner                     | <br>Date                                                                                    |  |  |  |

### SIMULATIONS

#### 4.1 Simulation 1: RLC circuit

| Specialisation:    | Power Systems   | Electronics      | $\square$ | Digital | × |  |

|--------------------|-----------------|------------------|-----------|---------|---|--|

| Name of learner: _ |                 |                  |           |         |   |  |

| Class:             | Date Completed: |                  | MARK      | 40      |   |  |

| Date Assessed:     |                 | Assessor Signatu | re:       |         |   |  |

| Date Moderated:    |                 | Moderator Signat | ure:      |         |   |  |

#### **PURPOSE:**

4.

To show the effect of changing frequency in an RLC circuit toward resonance.

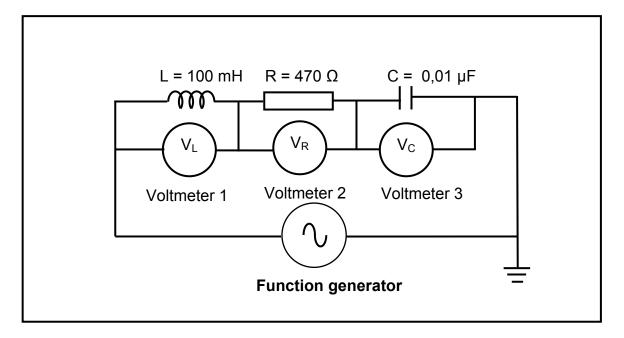

# ACTIVITY 1A: How $V_{\text{C}}$ and $V_{\text{L}}$ vary with frequency in a series RLC circuit

#### **REQUIRED:**

| TOOLS/INSTRUMENTS           | CONSUMABLES       |

|-----------------------------|-------------------|

| Breadboard/                 | 470 Ω resistor    |

| Dual-channel Oscilloscope   | 0.01 μF capacitor |

| Function Generator          | 100 mH inductor   |

| Multimeter (analog/digital) | Connecting wires  |

| Side cutters                |                   |

#### PROCEDURE:

1. Set the function generator to a sine wave and adjust the voltage to 5 V. Once the voltage is set do not change the amplitude setting of the voltage until all the experiments have been done.

Set the amplitude settings on the oscilloscope to the same for both channel 1 and channel 2.

Construct the circuit. Connect the multimeters and function generator, as shown in the RLC series circuit.

2. Adjust the frequency of the function generator until the voltmeter reading across the inductor and capacitor are the same. Record the reading of the voltages across each component and of the frequency on the table below.

| Reading of the frequency and voltages on the meters |   |  |  |  |  |

|-----------------------------------------------------|---|--|--|--|--|

| $V_L$                                               | = |  |  |  |  |

| V <sub>C</sub>                                      | = |  |  |  |  |

| $V_R$                                               | = |  |  |  |  |

| f                                                   | = |  |  |  |  |

**NOTE:** Readings on this table will be taken as reference values.

(4)

3. Adjust the frequency above the **reference values**.

Record the reading of the voltages across each component and of the frequency in the table below.

| Reading of     | the frequency and voltages on the meters |    |

|----------------|------------------------------------------|----|

| $V_L$          | =                                        |    |

| V <sub>C</sub> | =                                        |    |

| f              | =                                        | (3 |

4. Adjust the frequency below the **reference values**.

Record the reading of the voltages across each component and of the frequency on the table below.

| Reading of the frequency and voltages on the meters |   |  |  |

|-----------------------------------------------------|---|--|--|

| V <sub>L</sub>                                      | = |  |  |

| $V_{C}$                                             | = |  |  |

| f                                                   | = |  |  |

5. Connect the multimeters, oscilloscope and the function generator as shown on the RLC series circuit.

6. Adjust the frequency of the function generator until the reading across the inductor and capacitor are the same again. Record the readings on the voltmeters and ammeter and of the frequency on the table below.

| Reading on the meters |   |  |  |  |

|-----------------------|---|--|--|--|

| $V_L$                 | = |  |  |  |

| V <sub>C</sub>        | = |  |  |  |

| I <sub>T</sub>        | = |  |  |  |

| f                     | = |  |  |  |

(2)

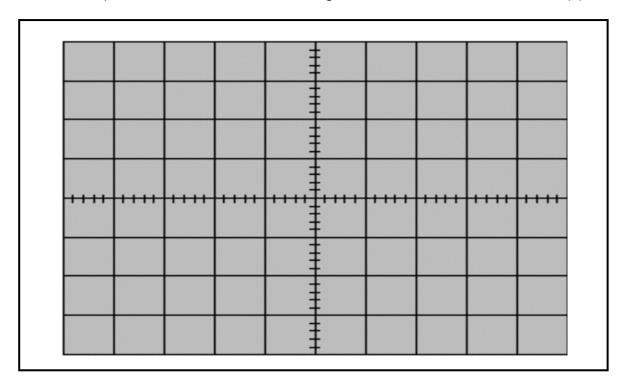

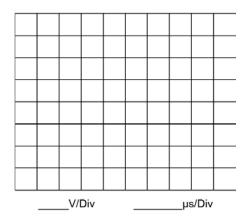

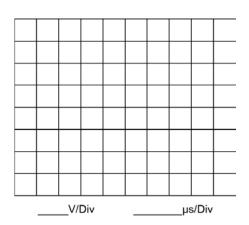

7. Draw the shape of the waveforms on the oscillogram.

(4)

# 8. **CONCLUSION:**

| With reference to the values in the tables and the waveforms on the oscillogram, | describe |

|----------------------------------------------------------------------------------|----------|

| the responses of the voltages across each component when the frequency is        | adjusted |

| above and below reference values.                                                |          |

(4)

SUBTOTAL – ACTIVITY A: [20]

(4)

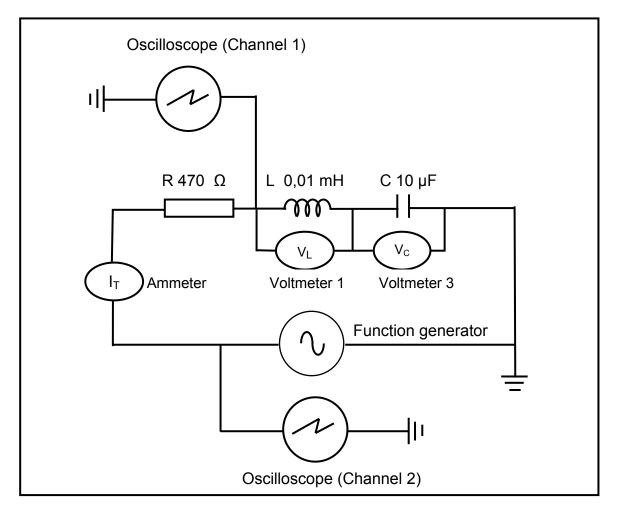

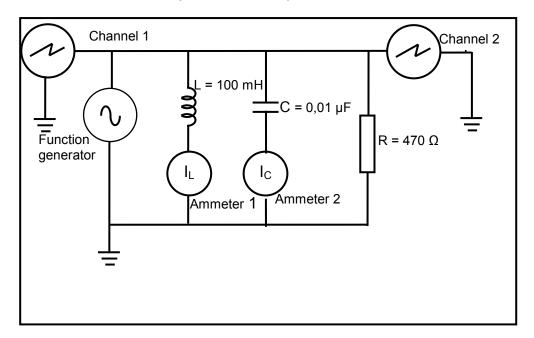

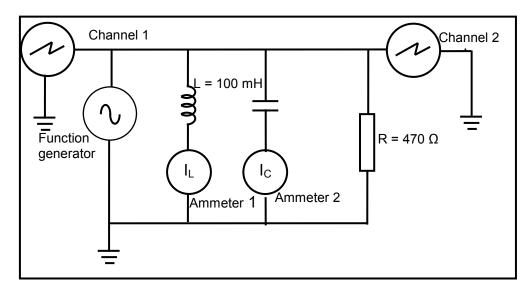

#### ACTIVITY 1B: How Ic and IL vary with frequency in a parallel RLC circuit

#### **REQUIRED:**

| TOOLS/INSTRUMENTS               | CONSUMABLES       |

|---------------------------------|-------------------|

| Breadboard/                     | 470 Ω resistor    |

| Dual-channel Oscilloscope       | 0.01 μF Capacitor |

| Function Generator              | 100 mH inductor   |

| Multimeter (analog/digital) x 3 | Connecting wires  |

| Side cutters                    | -                 |

| Wire stripper                   |                   |

#### PROCEDURE:

Set the function generator to a sine wave and adjust the voltage to 5 V. Once the voltage is set do not change the amplitude setting of the voltage. Set the amplitude settings on the oscilloscope to the same for both channel 1 and channel 2.

Connect the multimeters and function generator, as shown in the RLC series circuit.

2. Adjust the frequency of the function generator until the reading on ammeter 1 and ammeter 3 are the same. Record the reading through each component and of the frequency in the table below.

| Readings on the ammeters |   |  |  |  |  |

|--------------------------|---|--|--|--|--|

| IL                       | = |  |  |  |  |

| I <sub>C</sub>           | = |  |  |  |  |

| $I_R$                    | = |  |  |  |  |

| f                        | = |  |  |  |  |

**NOTE:** Readings on this table will be taken as reference values.

3. Adjust the frequency above the **reference values**. Record the values of the currents through the inductor and the capacitor and

| Readings on the ammeters |   |  |  |  |  |

|--------------------------|---|--|--|--|--|

| IL                       | = |  |  |  |  |

| I <sub>C</sub>           | = |  |  |  |  |

| f                        | = |  |  |  |  |

4. Adjust the frequency below the **reference values**.

the frequency on the table below.

Record the values of the current through each component and of the frequency on the table below.

| Readings on the ammeters |    |  |  |  |

|--------------------------|----|--|--|--|

| IL                       | II |  |  |  |

| I <sub>C</sub>           | =  |  |  |  |

| f                        | =  |  |  |  |

#### **PROCEDURE**

Connect the multimeters, function generator and the oscilloscope, as shown in the circuit below.

Adjust the frequency of the function generator until the reading through the inductor and a capacitor are the same. Record the readings through the ammeters and of the frequency on the table below.

| Readings on the ammeters |   |  |  |  |  |

|--------------------------|---|--|--|--|--|

| IL                       | = |  |  |  |  |

| I <sub>C</sub>           | = |  |  |  |  |

| f                        | = |  |  |  |  |

(3)

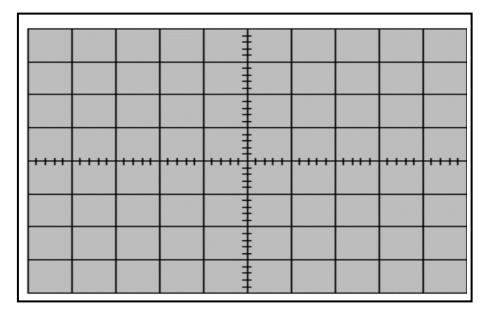

Draw the shape of the waveforms on the oscillogram.

#### **CONCLUSION:**

With reference to the values on the table and of the waveforms on the oscillogram, describe the responses of the current through each component when the frequency is adjusted above and below **reference values**.

(3)

[20]

SUBTOTAL – ACTIVITY 1A: 20 SUBTOTAL – ACTIVITY 1B: 20 TOTAL: 40

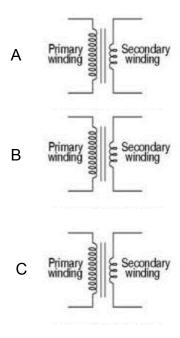

# 4.2 Simulation 2: Connecting three single-phase transformers to a three-phase supply

| Specialisation:    | Power Systems   ☑ | Electronics      | ×    | Digital | × |

|--------------------|-------------------|------------------|------|---------|---|

| Name of learner: _ |                   |                  | MARK |         |   |

| Class:             | Date Completed: _ |                  |      | 40      |   |

| Date Assessed:     | A                 | ssessor Signatu  | re:  |         |   |

| Date Moderated:    | N                 | Moderator Signat | ure: |         |   |

#### **PURPOSE:**

- To connect three identical single-phase step-down transformers in star-delta to a threephase supply

- To connect the secondary to a load that consist of three identical incandescent lamps that are connected in delta

- To measure the primary and secondary line and phase voltages and currents

#### **REQUIRED:**

| TOOLS/INSTRUMENTS/DEVICES              | CONSUMABLES                        |

|----------------------------------------|------------------------------------|

| Three identical step-down single-phase | Connecting wires                   |

| transformers                           | Three identical incandescent lamps |

| A three-phase supply                   |                                    |

| Clamp meter and multimeter             |                                    |

| Wire-striper                           |                                    |

| Long nose pliers                       |                                    |

| Screw driver                           |                                    |

| Side cutters                           |                                    |

#### PROCEDURE:

1. Connect the primary windings of each transformer to the supply and the secondary to the load (lamp).

Complete the table below by measuring the primary and secondary voltages of each single-phase transformer before connecting them in star-delta configuration.

**NOTE:** Use single phase to connect (neutral and live).

| Transformer | Primary voltage     | Secondary voltage  |

|-------------|---------------------|--------------------|

| Α           | V <sub>Prim</sub> = | V <sub>SEC</sub> = |

| В           | V <sub>Prim</sub> = | V <sub>SEC</sub> = |

| С           | V <sub>Prim</sub> = | V <sub>SEC</sub> = |

(6)

2. Calculate the transformer ratio of each single-phase transformer using voltage values from the table above.

Explain whether these three transformers can be connected in star-delta configuration.

**NOTE:** Your answer must be informed by transformer ratio calculations. (11)

3. Draw the circuit diagram in which these transformers are connected in a star/delta configuration using the colour coding and label it correctly.

4. Connect three identical single-phase step-down transformers in star-delta to a three-phase supply.

Connect the primary (star) to the three-phase supply and the secondary (delta) to a load that consists of three identical incandescent lamps. The lamps must be connected in delta too.

#### NOTE:

- The secondary voltage of the transformer is not critical. The only requirement is that the secondary voltage and the voltage of the lamps are compatible.

- It is the duty of the teacher to verify that the learners are connecting the transformers correctly, before connecting the mains supply. If you are not entirely sure of your connections DO NOT SWITCH ON. Test for short circuits.

- Mains supply can be lethal. Be extremely careful.

- Schools using older panels that are closed up and schools with no clamp meters should measure the primary line and phase voltages only.

- 5. Measure the primary and secondary line and phase voltages and currents. Record the reading on the table below.

| Primary side               | Secondary side       |                   |                          |                   |  |

|----------------------------|----------------------|-------------------|--------------------------|-------------------|--|

| Reading between line volta | Reading between line |                   |                          |                   |  |

| currents                   |                      |                   | voltage and line current |                   |  |

| $V_{L1} \& V_{L2} =$       | $V_{L1} \& N =$      | I <sub>L1</sub> = | $V_{L1} \& V_{L2} =$     | I <sub>L1</sub> = |  |

| $V_{L1} \& V_{L2} =$       | $V_{L2} \& N =$      | I <sub>L2</sub> = | $V_{L1} \& V_{L2} =$     | I <sub>L2</sub> = |  |

| $V_{L1} \& V_{L2} =$       | $V_{L3} \& N =$      | I <sub>L3</sub> = | $V_{L1} \& V_{L2} =$     | I <sub>L3</sub> = |  |

(15)

#### **CONCLUSION:**

Your conclusion must be based on the table above and other observations.

(4) **[40]**

# 4.3 Simulation 3: Inspecting and testing the AC motor

| Specialisation:                                                                                 | Power Systems | Ø       | Electronics       | ×         | Digital 🗷 |

|-------------------------------------------------------------------------------------------------|---------------|---------|-------------------|-----------|-----------|

| Name of learner: _                                                                              |               |         |                   |           |           |

| Class:                                                                                          | Date Comp     | leted:  |                   | MARK<br>- | 40        |

| Date Assessed:                                                                                  |               |         | Assessor Signatu  | re:       |           |

| Date Moderated:                                                                                 |               |         | Moderator Signat  | ure:      |           |

| PURPOSE:                                                                                        |               |         |                   |           |           |

| <ul><li>To conduct the following</li><li>Visual mechanic</li><li>Electrical inspector</li></ul> | •             | tor usi | ng measuring inst | ruments   |           |

# **REQUIRED RESOURCES:**

| TOOLS/INSTRUMENTS                              | CONSUMABLES |

|------------------------------------------------|-------------|

| Three-phase AC motor                           |             |

| Multimeter                                     |             |

| <ul> <li>Insulation tester (Megger)</li> </ul> |             |

#### **PROCEDURE:**

Use the list below to conduct an inspection tests on an AC electrical motor. Complete the results in the table below.

#### **ACTIVITY 1A:**

| 1.1 | Details on the nameplate of | of the motor being tested: |         |

|-----|-----------------------------|----------------------------|---------|

|     | Phase:                      | Supply voltage:            |         |

|     | Pole pairs:                 |                            | <u></u> |

|     | Efficiency:                 | Current:                   |         |

|     | Power rating:               | Frequency:                 |         |

# **ACTIVITY 1B:** Complete the table below.

| DESCRIPTION                                          | VISUAL INSPECTION AND READINGS TAKEN (Megger)  | MARKS<br>ALLOCATED |

|------------------------------------------------------|------------------------------------------------|--------------------|

|                                                      | ondition of windings: Measurements taken       |                    |

|                                                      | est 1: Continuity of the windings (3 marks)    |                    |

| A1 – A2                                              |                                                |                    |

| B1 – B2                                              |                                                |                    |

| C1 – C2                                              |                                                |                    |

| Test 2: li                                           | nsulation resistance between windings (3 mar   | ks)                |

| A1 – B1                                              |                                                |                    |

| A1 – C1                                              |                                                |                    |

| B1 – C1                                              |                                                |                    |

| Tes                                                  | t 3 – Insulation resistance to earth (3 marks) |                    |

| A1 – Earth                                           |                                                |                    |

| B1 – Earth                                           |                                                |                    |

| C1 – Earth                                           |                                                |                    |

|                                                      | Test 4 – Mechanical inspection                 |                    |

| N                                                    | ote all errors (9 marks) (Short description)   |                    |

| 1.5                                                  | Condition of rotor and shaft                   | 1                  |

| Key/Key way                                          |                                                |                    |

| Front bearing                                        |                                                |                    |

| Back bearing                                         |                                                |                    |

| Co                                                   | ondition of motor frame (Short description)    |                    |

| Condition of termination box                         |                                                |                    |

| Flange/Foot mount                                    |                                                |                    |

| Front/Back-end shield                                |                                                |                    |

| Stator/Field housing                                 |                                                |                    |

| Mounting bolts and nuts/screws                       |                                                |                    |

| Condition of cooling fan, fan cover and cooling fins |                                                |                    |

| ian sover and econing into                           |                                                | l .                |

(18)

1.3

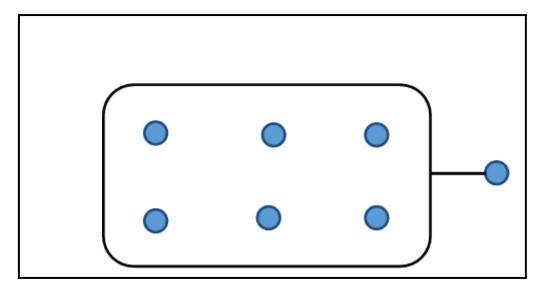

1.2.2 Draw and label the correct connection of internal wiring on the diagram provided below. (This information must correspond with the internal wiring of the motor tested.)

1.2.3 According to the regulation, state the minimum acceptable values of the following:

1.2.3.1 Continuity test of the windings:

(1)

(4)

1.2.3.2 Insulation resistance test between windings:

(1)

Conducted Test Acceptable/Not acceptable with reason

Winding resistance

Insulation resistance

Earth resistance

Can the motor be used

(8) **[40]**

# 4.4 Simulation 4: DOL Starter

| Specialisation:    | Power Systems 🛮 🗹 | Electronics       | ×         | Digital | × |

|--------------------|-------------------|-------------------|-----------|---------|---|

| Name of learner: _ |                   |                   |           |         |   |

| Class:             | Date Completed:   |                   | MARK<br>- | 40      |   |

| Date Assessed:     |                   | Assessor Signatu  | re:       |         |   |

| Date Moderated:    |                   | Moderator Signate | ure:      |         |   |

#### **PURPOSE:**

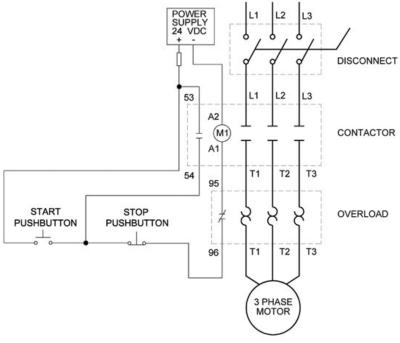

Practical simulation of a three-phase direct-on-line (DOL) starter

# **REQUIRED:**

| TOOLS/INSTRUMENTS                                                                                                                                                                                          | CONSUMABLES                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 1 x three-phase contactor with auxiliary contacts 1 x three-phase overload relay 1 x stop button 1 x start button 1 x 380 V delta induction motor (squirrel-cage motor) Correct wire size or plug in leads | Multimeter or continuity tester 2 x pilot lights (red and green) |

| Wire stripper Long nose pliers Screw driver Side cutters                                                                                                                                                   |                                                                  |

# NSC

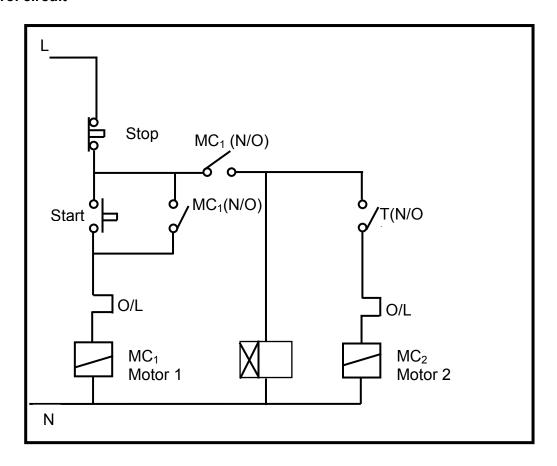

#### CONTROL AND POWER CIRCUIT OF THE DOL

#### PROCEDURE:

Wire the control circuit first; test it before wiring and connecting it to the power circuit.

Connect the motor to the power circuit and set the overload.

Now ask the teacher to check the circuits. When the circuits are correct switch the supply on and start the motor.

Stop the motor and switch the supply off.

Consider all safety aspect before and during the wiring process and be focused until the motor is cooperating.

The teacher will insert faults on the control circuit and the learner must identify them.

#### **ACTIVITY 1A:**

1.1 State why the normally hold-in contact is connected in parallel with the start button. (2) 1.2 Describe the functions of the following: 1.2.1 Overload relay (2) 1.2.2 Contactor (2) 1.3 State any TWO precautionary measures to adhere to when wiring the circuit. (2) 1.4 Change the direction of rotation of the motor and state your observation. (2) 1.5 State TWO applications of a DOL starter. (2)

[12]

**FACET: Simulation 4: DOL starter**

| FACETS                        | FACET 1                                                                       | FACET 2                                       | FACET 3                                                     | FACET 4                                     | MAXIMUM<br>POSSIBLE<br>MARKS | LEARNER'S<br>MARK |

|-------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------|---------------------------------------------|------------------------------|-------------------|

| Preparation of the simulation | Correctly interprets<br>the wiring diagram of<br>control and power<br>circuit | Correctly identifies and collects all devices | Correctly identifies and collects all measuring instruments | Correctly identifies and collects all tools | 8                            |                   |

| Wiring of control circuit     | Tests the functionality of all devices to be used                             | Correct procedure in wiring the circuit       | Tests continuity in the circuit                             | Operation of the circuit                    | 8                            |                   |

| Wiring of power circuit       | Tests the functionality of the motor                                          | Correct procedure in wiring the circuit       | Tests continuity in the circuit                             |                                             | 6                            |                   |

| Setting of fault              |                                                                               |                                               |                                                             | Fault successfully identified               | 2                            |                   |

| Safety                        |                                                                               |                                               |                                                             | Safety precautions were observed            | 2                            |                   |

| Housekeeping                  |                                                                               |                                               |                                                             | Housekeeping was practised                  | 2                            |                   |

|                               |                                                                               |                                               |                                                             |                                             | (28)                         |                   |

|                               |                                                                               |                                               |                                                             | Activity 1A                                 | (12)                         |                   |

|                               |                                                                               |                                               |                                                             | Facet                                       | (28)                         |                   |

|                               |                                                                               |                                               |                                                             | TOTAL                                       | 40                           |                   |

|                               |                                                                               |                                               |                                                             |                                             |                              |                   |

# 4.5 Simulation 5: Three-phase sequence motor control starter with overload and timer using PLC

| Specialisation:    | Power Systems 🛮 🗹 | Electronics       | ×           | Digital | × |

|--------------------|-------------------|-------------------|-------------|---------|---|

| Name of learner: _ |                   |                   | [           |         |   |

| Class:             | Date Completed    | :                 | MARK  <br>_ | <br>40  |   |

| Date Assessed:     |                   | Assessor Signatu  | re:         |         |   |

| Date Moderated:    |                   | Moderator Signatu | ure:        |         |   |

#### **PURPOSE:**

Practical simulation of a three-phase sequence motor control starter with overload and timer using PLC

#### **Control circuit**

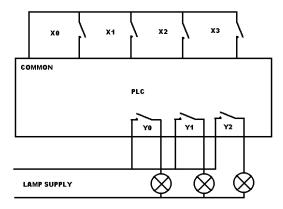

# PLC unit with inputs and outputs

X1 = Stop X2=Start X3=O/L 1 X4 = O/L 2

Lamp 1 = Circuit is ON

Lamp 2 = Motor 1

Lamp 3 = Motor 2

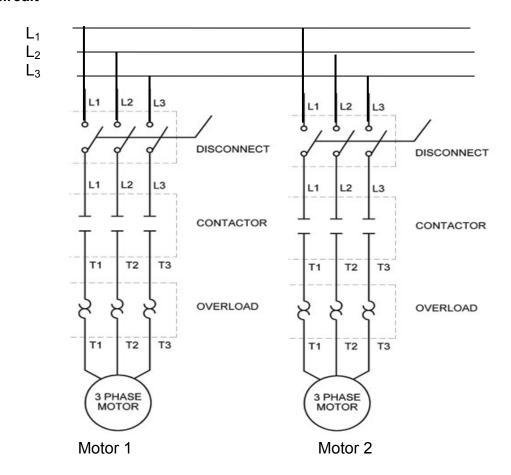

#### **Power circuit**

(4)

(2)

#### **RESOURCES:**

| TOOLS/INSTRUMENTS                                  | MATERIALS                        |

|----------------------------------------------------|----------------------------------|

| 2 x three-phase contactors with auxiliary contacts | Connecting wires                 |

| 2 x three-phase overload relays                    | 3 x pilot lights (red and green) |

| 1 x stop button                                    |                                  |

| 1 x start button                                   |                                  |

| 2 x three-phase induction motors                   |                                  |

| Multimeter/Clamp meter or continuity tester        |                                  |

| PLC unit                                           |                                  |

| Computer/Programmer                                |                                  |

| Wire-striper                                       |                                  |

| Long nose pliers                                   |                                  |

| Screw driver                                       |                                  |

| Side cutters                                       |                                  |

#### PROCEDURE:

- Convert the control circuit of a sequence motor control starter with overload and timer into a ladder logic diagram.

- Connect the PLC to control the motor.

- Run the PLC program and simulate the operation.

- Program the ladder logic diagram through a computer and load the program to the PLC.

- Do not switch on the supply before the teacher has checked the circuit.

- When the circuits are correct switch the supply on.

- Run the PLC program to start the motor.

- The teacher will insert faults on the PLC and the learner must identify them.

#### THE OPERATION:

When the start button is pressed, motor 1 starts rotating. After 10 seconds motor 2 also starts rotating. Both motors must be stopped by a stop button, if they trip from overload. Load the program from the computer to the PLC. Connect the PLC to control the motors. The teacher should create faults on the PLC program for the participants to identify.

#### **ACTIVITY**

| 1.1 | Snapshot the programmed ladder logic diagram and paste it on the blank page. |

|-----|------------------------------------------------------------------------------|

|     |                                                                              |

|     |                                                                              |

|     |                                                                              |

|     |                                                                              |

|     |                                                                              |

|     |                                                                              |

|     |                                                                              |

|     |                                                                              |

|     |                                                                              |

|     |                                                                              |

|     |                                                                              |

1.2 Explain why the overload relay is connected to each motor.

# Facet: Three-phase sequence motor control starter with overload and timer using PLC

| FACETS                    | FACET 1                                                             | FACET 2                                                         | FACET 3                                                  | FACET 4                             | MAXIMUM<br>POSSIBLE<br>MARKS | LEARNERS<br>MARK |

|---------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------|-------------------------------------|------------------------------|------------------|

| Preparation of            | Correctly interpreting the                                          | Correctly identifying                                           | Correctly identifying and                                | Correctly identifying               | 8                            |                  |

| the simulation            | wiring diagram of control and power circuit                         | and collecting all devices                                      | collecting all measuring instruments                     | and collecting all tools            |                              |                  |

| Wiring of control circuit | Testing the functionality of all devices to be used                 | Correct procedure in wiring the circuit                         | Testing continuity in the circuit                        | Operation of the circuit            | 8                            |                  |

| PLC unit                  | Programming the ladder logic diagram in the computer and is running | Correctly loading the program from the computer to the PLC unit | Correctly connecting the PLC unit to control the circuit | Run the program to start the motor. | 8                            |                  |

| Wiring of Power circuit   | Testing the functionality of the motor                              | Correct procedure in wiring the circuit                         | Testing continuity in the circuit                        |                                     | 6                            |                  |

| Safety                    |                                                                     |                                                                 |                                                          | Safety precautions were observed    | 2                            |                  |

| House<br>keeping          |                                                                     |                                                                 |                                                          | Housekeeping was practised          | 2                            |                  |

|                           |                                                                     |                                                                 |                                                          |                                     | (34)                         |                  |

|                           |                                                                     |                                                                 |                                                          | Activity                            | (6)                          |                  |

|                           |                                                                     |                                                                 |                                                          | Facet                               | (34)                         |                  |

|                           |                                                                     |                                                                 |                                                          | Total                               | 40                           |                  |

#### 4.6 Simulation 6: The field-effect transistor

| Specialisation:    | Power Systems 🗷   | Electronics        | $\square$ | Digital | X |

|--------------------|-------------------|--------------------|-----------|---------|---|

| Name of learner: _ |                   |                    | MARK      |         |   |

| Class:             | _ Date Completed: |                    | WARK      | 40      |   |

| Date Assessed:     |                   | Assessor Signature | e:        |         |   |

| Date Moderated:    |                   | Moderator Signatur | e:        |         |   |

#### **PURPOSE:**

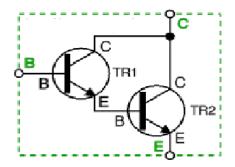

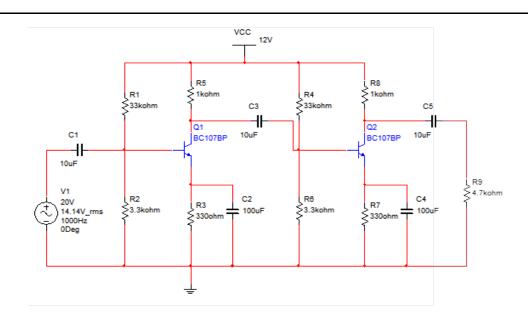

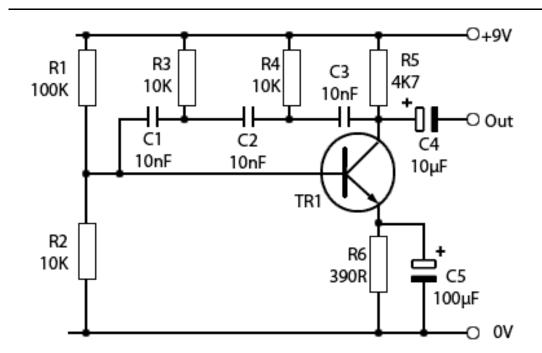

Construct simple circuits using JFETs and MOSFETs and display the input/output waveforms on an oscilloscope

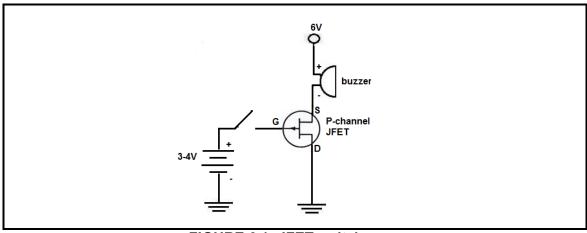

#### ACTIVITY 6A: Construct a circuit using a JFET as a switch

#### **REQUIRED:**

| TOOLS/INSTRUMENTS        | CONSUMABLES                                |

|--------------------------|--------------------------------------------|

| Analogue/Digital trainer | 1 x 6 V buzzer                             |

| Multimeter x 2           | 1 x J176 JFET P channel (Any suitable JFET |

| Variable DC power supply | may be used)                               |

| Side cutter              | Connecting wires                           |

| Wire stripper            |                                            |

#### PROCEDURE:

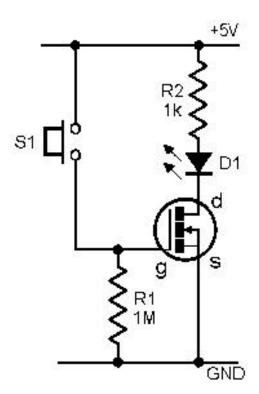

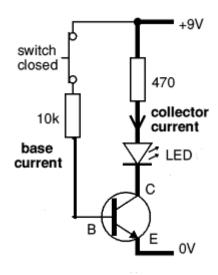

1. Connect the circuit on the breadboard, as shown in FIGURE 6.1.

FIGURE 6.1: JFET switch

2. Close the switch and observe the output of the buzzer. Record your observation (2)

| CONCLUSION:     |                         |                |                 |                  |

|-----------------|-------------------------|----------------|-----------------|------------------|

|                 | he deduced from your ob | convotion with | rogard to a IEE | T oo o owitch    |

| xplain what can | be deduced from your ob | servation with | regard to a JFE | : I as a switch. |

# FACET SHEET 6A: Construct a circuit using a JFET as a switch

|                                                             | FACET 1                                          | FACET 2                                         | FACET 3                                            | FACET 4            | MAXIMUM<br>POSSIBLE<br>MARKS | LEARNER<br>MARK |

|-------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------|----------------------------------------------------|--------------------|------------------------------|-----------------|

| Prepare for the simulation                                  | Identifies components correctly                  | Collect<br>PSU/MiniTrainer                      | Collect instruments – oscilloscope                 | Collect hand tools | 4/2 = 1                      |                 |

| Hand tools                                                  | Uses side cutters correctly                      | Use wire stripper correctly                     |                                                    |                    | 2/2 = 1                      |                 |

| Preparation for insertion of components on breadboard.      | Check the datasheet on the FET (1)               | Set supply voltage correct at 6 V (1)           | Set input voltage correct at 3–4 V (1)             |                    | 3                            |                 |

| Correct connection on<br>Breadboard – nodes and<br>polarity | 6 nodes for correct connection (6/2 = 3)         | Polarity of buzzer – correct (1)                | Polarity of JFET correct (2)                       |                    | 6/2 = 3                      |                 |

| Circuit is working correctly                                | Switch = ON<br>Buzzer is OFF (1)                 | Switch = OFF<br>Buzzer is ON (1)                |                                                    |                    | 2                            |                 |

| Connection of meters                                        | Connection of MM across input to show 3 V/On/Off | Connection of MM<br>across output =<br>High/Low |                                                    |                    | 2                            |                 |

| Housekeeping                                                | Cleaning the work area after the experiment (1)  | Return tools to correct places after work (1)   | Disposing off waste materials correctly after work |                    | 2/2 = 1                      |                 |

| Safety                                                      | Observing safety before being reminded (2)       | Observing safety after being reminded (1)       | Not observing safety (0)                           |                    | 2/2 = 1                      |                 |

| TOTAL                                                       | ` `                                              |                                                 |                                                    |                    | 14                           |                 |

# ACTIVITY 6B: Connect a circuit using a MOSFET as a switch

#### **REQUIRED:**

| TOOLS/INSTRUMENTS             | MATERIALS            |

|-------------------------------|----------------------|

| Analogue/Digital trainer      | 1 x 1 KΩ resistor    |

| Analogue/Digital oscilloscope | 1 x MΩ resistor      |

| Function generator            | 1 x BS 270 N channel |

| Variable DC power supply      | 1 x LED              |

| Side cutters                  | 1 x toggle switch    |

| Wire stripper                 | Connecting wires     |

|                               |                      |

# PROCEDURE:

1. Construct the circuit as shown in the circuit below.

| 2. | Close the switch and observe the output of the LED. Record your findings | (1) |

|----|--------------------------------------------------------------------------|-----|

| 3. | Open the switch and observe the output of the LED. Record your findings  | (1) |

|    |                                                                          |     |

| CONCLUSION:                                                          |                  |

|----------------------------------------------------------------------|------------------|

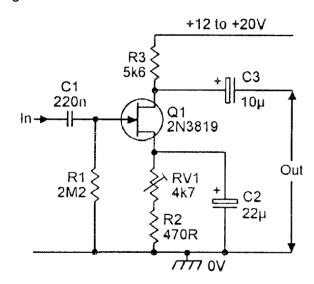

| Explain what can be deduced from your observation with regard switch | d to a MOSFET as |